# Copyright

This documentation and the software included with this product are copyrighted 2001 by Advantech Co., Ltd. All rights are reserved. Advantech Co., Ltd. reserves the right to make improvements in the products described in this manual at any time without notice. No part of this manual may be reproduced, copied, translated or transmitted in any form or by any means without the prior written permission of Advantech Co., Ltd. Information provided in this manual is intended to be accurate and reliable. However, Advantech Co., Ltd. assumes no responsibility for its use, nor for any infringements of the rights of third parties which may result from its use.

# Acknowledgments

PC-LabCard is a trademark of Advantech Co., Ltd. IBM and PC are trademarks of International Business Machines Corporation. MS-DOS, Windows, Microsoft Visual C++ and Visual BASIC are trade-marks of Microsoft Corporation. Intel and Pentium are trademarks of Intel Corporation. Delphi and C++ Builder are trademarks of Inprise Corporation.

#### CE notification

The PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L, developed by ADVANTECH CO., LTD., has passed the CE test for environmental specifications when shielded cables are used for external wiring. We recommend the use of shielded cables. This kind of cable is available from Advantech. Please contact your local supplier for ordering information.

# **On-line Technical Support**

For technical support and service, please visit our support website at: http:\\www.advantech.com/support

Part No. 2003171600 1st Edition

Printed in Taiwan June 2001

# **Contents**

| 1. I | ntroduction                    | 1  |

|------|--------------------------------|----|

| 1.1  | Features                       | 2  |

| 1.2  | Installation Guide             | 4  |

| 1.3  | Software                       | 6  |

| 1.4  | Accessories                    | 6  |

| 2. I | nstallation                    | 9  |

| 2.1  | Unpacking                      | 9  |

| 2.2  | Driver Installation            | 11 |

| 2.3  | Hardware Installation          | 13 |

| 2.4  | Device Setup & Configuration   | 15 |

| 2.5  | Device Testing                 | 19 |

| 3. S | Signal Connections             | 23 |

| 3.1  | Overview                       | 23 |

| 3.2  | I/O Connector                  | 23 |

| 3.3  | Analog Input Connections       | 26 |

| 3.4  | Analog Output Connections      |    |

| 3.5  | Trigger Source Connections     | 30 |

| 3.6  | Field Wiring Considerations    | 31 |

| 4. 8 | Software Overview              | 33 |

| 4.1  | Programming Choices            | 33 |

| 4.2  | DLL Driver Programming Roadmap |    |

| <b>5.</b> C | alibration 37                                   |

|-------------|-------------------------------------------------|

| 5.1         | PCI-1710/1710L/1710HG/1710HGL Calibration 38    |

| 5.2         | PCI-1711/1711L Calibration                      |

| 5.3         | PCI-1716/1716L Calibration                      |

| App         | pendix A. Specifications 55                     |

| App         | endix B. Block Diagram 65                       |

| C. R        | Register Structure and Format 69                |

| <b>C.1</b>  | Overview 69                                     |

| <b>C.2</b>  | I/O Port Address Map70                          |

| C.3         | Channel Number and A/D Data - BASE+0 and BASE+1 |

| <b>C.4</b>  | Software A/D Trigger - BASE+077                 |

|             | A/D Channel Range Setting - BASE+278            |

| <b>C.6</b>  | MUX Control - BASE+4 and BASE+581               |

| <b>C.7</b>  | Control Register - BASE+6 83                    |

| <b>C.8</b>  | Status Register - BASE+6 and BASE+785           |

| <b>C.9</b>  | Clear Interrupt and FIFO - BASE+8 and BASE+9 86 |

| <b>C.10</b> | D/A Output Channel 0 - BASE+10 and BASE+11 86   |

| C.11        | D/A Output Channel 0 - BASE+10 and BASE+11 87   |

| C.12        | D/A Output Channel 1 - BASE+12 and BASE+13 87   |

| C.13        | D/A Output Channel 1 - BASE+12 and BASE+13 88   |

| <b>C.14</b> | D/A Reference Control -BASE+1489                |

| C.15        | Digital I/O Registers - BASE+16 and BASE+17 90  |

| <b>C.16</b> | Calibration Registers - BASE+18 and BASE+19 91  |

| C.17        | Board ID Registers - BASE+2092                  |

| C.18       | Programmable Timer/Counter Registers BASE+24, BASE+26, BASE+28 and BASE+30 |

|------------|----------------------------------------------------------------------------|

| App        | pendix D. 82C54 Counter Function 93                                        |

| <b>D.1</b> | The Intel 82C54                                                            |

| <b>D.2</b> | Counter Read/Write and Control Registers94                                 |

| <b>D.3</b> | Counter Operating Modes96                                                  |

| <b>D.4</b> | Counter Operations                                                         |

|            | pendix E. PCI-1716/1716L Calibration nually)                               |

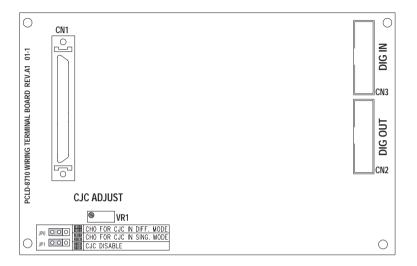

| App        | endix F. Screw-terminal Bord 107                                           |

| <b>F.1</b> | Introduction 107                                                           |

| <b>F.2</b> | Features 107                                                               |

| <b>F.3</b> | <b>Applications 108</b>                                                    |

| <b>F.4</b> | Board Layout 108                                                           |

| <b>F.5</b> | Pin Assignment 109                                                         |

| <b>F.6</b> | Technical Diagram 110                                                      |

# **Figures**

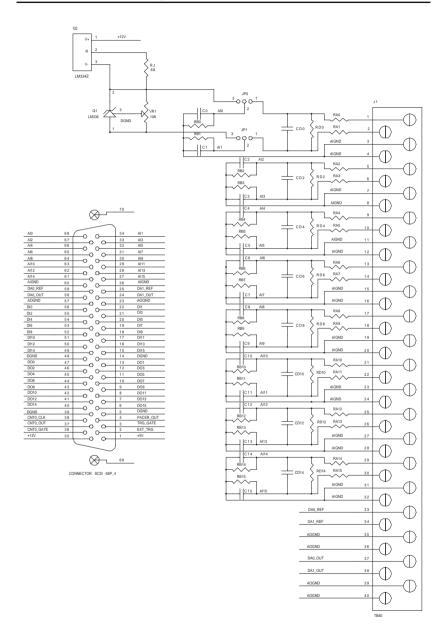

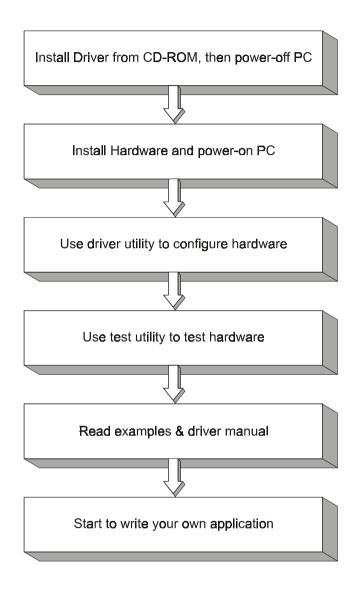

| Figure 1-1:                | Installation Flow Chart                                      | 5  |

|----------------------------|--------------------------------------------------------------|----|

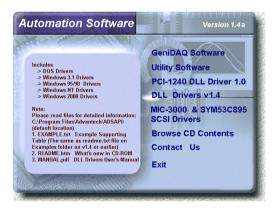

| Figure 2-1:                | The Setup Screen of Advantech Automation Software            | 11 |

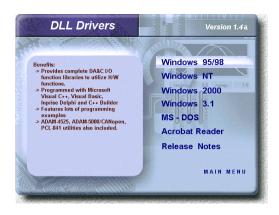

| Figure 2-2:                | Different options for Driver Setup                           | 12 |

| Figure 2-3:                | The device name listed on the Device Manager                 | 14 |

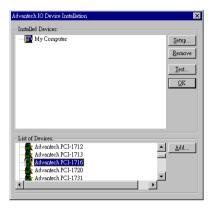

| Figure 2-4:                | The Advantech Device Installation utility program            | 15 |

| Figure 2-5:                | The I/O Device Installation dialog box                       | 16 |

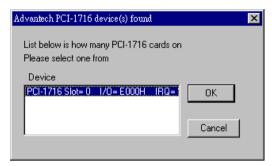

| Figure 2-6:                | The "Device(s) Found" dialog box                             | 17 |

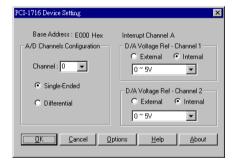

| Figure 2-7:                | The Device Setting dialog box                                | 17 |

| Figure 2-8:                | The Device Name appearing on the list of devices box         | 18 |

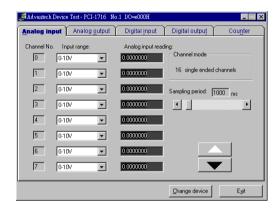

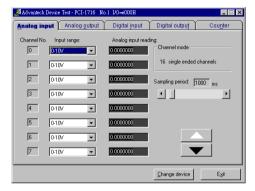

| Figure 2-9:                | Analog Input tab on the Device Test dialog box               | 19 |

| Figure 2-10:               | Analog Input tab on the Device Test dialog box               | 20 |

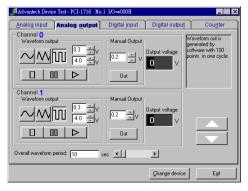

| Figure 2-11:               | Analog Output tab on the Device Test dialog box              | 20 |

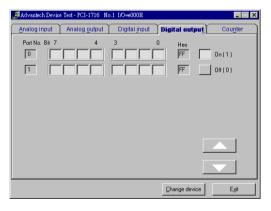

| <b>Figure 2-13:</b>        | Digital Output tab on the Device Test dialog box             | 21 |

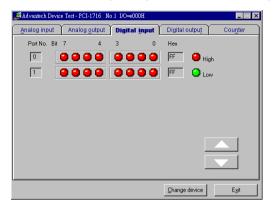

| <b>Figure 2-12:</b>        | Digital Input tab on the Device Test dialog box              | 21 |

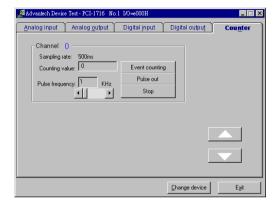

| <b>Figure 2-14:</b>        | Counter tab on the Device Test dialog box                    | 22 |

| Figure 3-1:                | I/O connector pin assignments for the PCI-1710/1710L/        |    |

|                            | 1710HG/1710HGL/1711/1711L/1716/1716L                         |    |

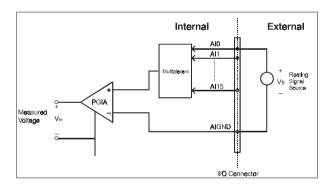

| Figure 3-2:                | Single-ended input channel connection                        | 26 |

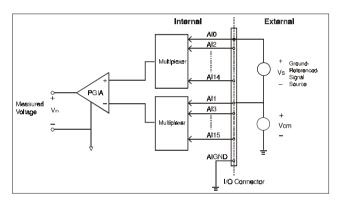

| Figure 3-3:                | Differential input channel connection - ground reference     |    |

|                            | signal source                                                |    |

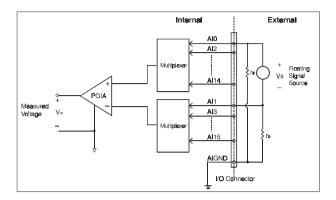

| Figure 3-4:                | Differential input channel connection - floating signal sour |    |

| Figure 3-5:                | Analog output connections                                    |    |

| Figure 5-3:                | PCI-1710/1710L/1710HG/1710HGL VR assignment                  |    |

| Figure 5-1:<br>Figure 5-2: | PCI-1711/1711L VR assignment                                 |    |

| Figure 5-2:                | PCI-1716/1716L VR assignment                                 |    |

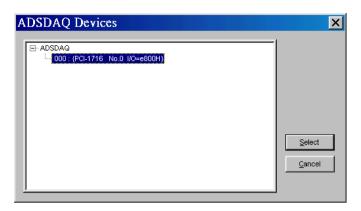

| Figure 5-4:                | Selecting the device you want to calibrate                   |    |

| _                          |                                                              |    |

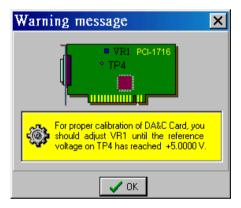

| Figure 5-5:                | Warning message before start calibration                     |    |

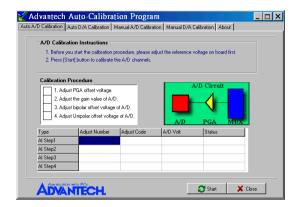

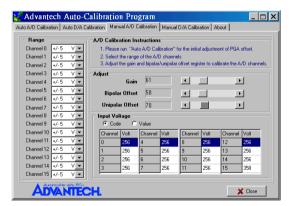

| Figure 5-6:                | Auto A/D Calibration Dialog Box                              |    |

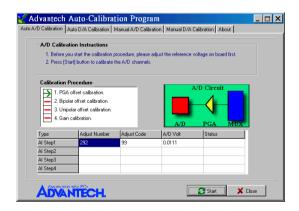

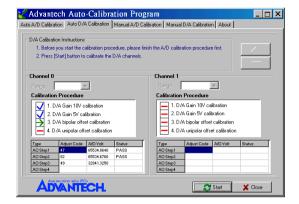

| Figure 5-7:                | A/D Calibration Procedure 1                                  |    |

| Figure 5-8:                | A/D Calibration Procedure 2                                  | 47 |

| Figure 5-9:         | A/D Calibration Procedure 3                            | 47 |

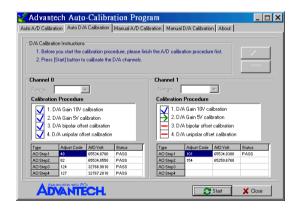

|---------------------|--------------------------------------------------------|----|

| Figure 5-11:        | Range Selection in D/A Calibration                     | 48 |

| Figure 5-10:        | A/D Calibration is finished                            | 48 |

| Figure 5-12:        | Calibrating D/A Channel 0                              | 49 |

| Figure 5-13:        | Calibrating D/A Channel 1                              | 49 |

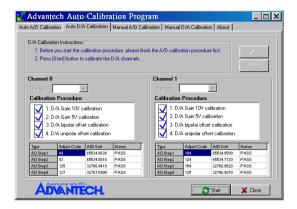

| Figure 5-14:        | D/A Calibration is finished                            | 50 |

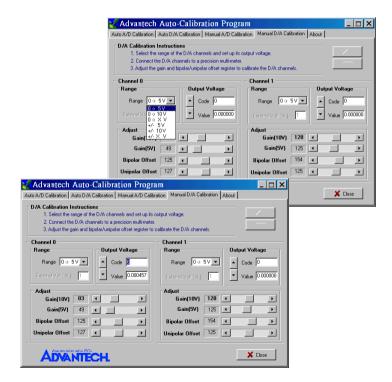

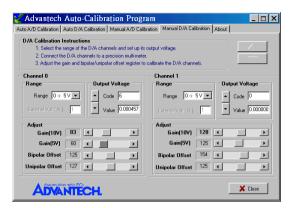

| Figure 5-15:        | Selecting Input Rage in Manual A/D Calibration panel   | 51 |

| Figure 5-16:        | Adjusting registers                                    | 51 |

| Figure 5-17         | & Figure 5-18: Selecting D/A Range and Choosing Output |    |

|                     | Voltage                                                | 52 |

| <b>Figure 5-19:</b> | Adjusting registers                                    | 53 |

|                     |                                                        |    |

# **Tables**

| Table 3-1:         | I/O Connector Signal Description                       | 25   |

|--------------------|--------------------------------------------------------|------|

| Table C-1:         | PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/         |      |

|                    | 1716L register format (Part 3)                         | 72   |

| Table C-1:         | PCI-1710/1710L/1710HG/1710HGL/1711/1711L register      |      |

|                    | format (Part 4)                                        |      |

| Table C-1:         | PCI-1716/1716L register format (Part 5)                | 74   |

| Table C-1:         | PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/         |      |

|                    | 1716L register format (Part 6)                         |      |

| Table C-3:         | PCI-1716/1716L Register for A/D data                   | 76   |

| Table C-2:         | PCI-1710/1710L/1710HG/1710HGL/1711/1711L Register      |      |

|                    | for channel number and A/D data                        |      |

| Table C-4:         | Register for A/D channel range setting                 | 78   |

| Table C-5:         | Gain codes for PCI-1710/1710L                          | .79  |

| Table C-6:         | Gain codes for PCI-1710HG/1710HGL                      | 80   |

| Table C-7:         | Gain codes for PCI-1711/1711L                          | .80  |

| Table C-8:         | Register for multiplexer control                       | .81  |

| Table C-9:         | Control Register                                       | 83   |

| Table C-10:        | Status Register                                        | 85   |

| Table C-11:        | Register to clear interrupt and FIFO                   | . 86 |

| Table C-12:        | Register for load D/A channel 0 data                   | 86   |

| Table C-13:        | Register for D/A channel 0 data                        | 87   |

| Table C-14:        | Register for load D/A channel 1 data                   | . 87 |

| Table C-15:        | Register for D/A channel 1 data                        | . 88 |

| <b>Table C-16:</b> | PCI-1710/1710HG/1711 Register for D/A reference contro |      |

|                    |                                                        | 89   |

| <b>Table C-17:</b> | PCI-1716 Register for D/A reference control            | .89  |

| <b>Table C-18:</b> | Register for digital input                             | .90  |

| <b>Table C-19:</b> | Register for digital output                            | 90   |

| Table C-20:        | Calibration Command and Data Register                  | .91  |

| Table C-21: | Calibration Command and Data Register | 91  |

|-------------|---------------------------------------|-----|

| Table C-22: | Register for Board ID                 | 92  |

|             |                                       |     |

| Table E-1:  | A/D binary code table                 | 102 |

| Table E-2:  | D/A binary code table                 | 105 |

# 1. Introduction

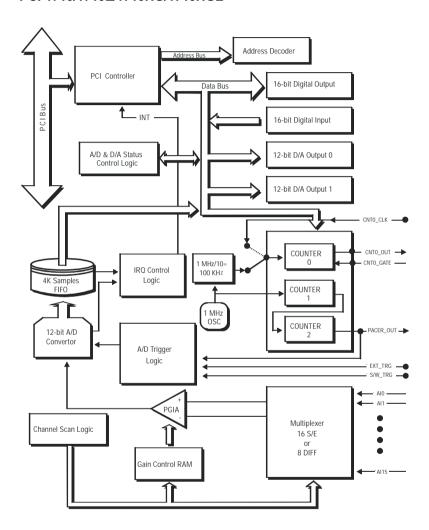

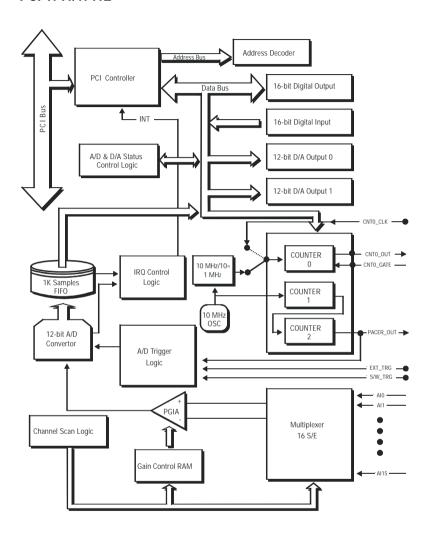

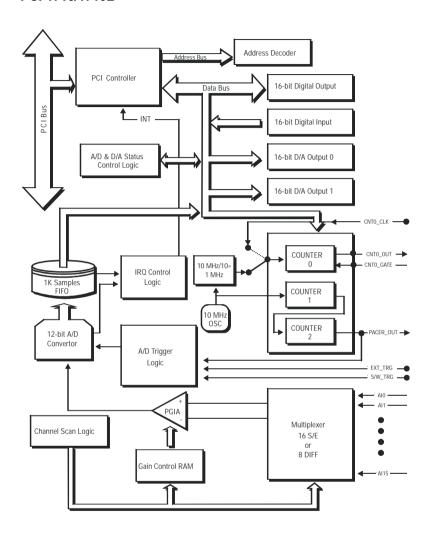

Thank you for buying the Advantech PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L PCI card. The Advantech PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716L is a powerful data acquisition (DAS) card for the PCI bus. It features a unique circuit design and complete functions for data acquisition and control, including A/D conversion, D/A conversion, digital input, digital output, and counter/timer. PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L provides specific functions for different user requirements:

| PCI-1710    | 12-bit, 100kS/s Multifunction card                                                           |

|-------------|----------------------------------------------------------------------------------------------|

| PCI-1710L   | 12-bit, 100kS/s Multifunction card w/o analog output                                         |

| PCI-1710HG  | 12-bit, 100kS/s High-Gain Multifunction card                                                 |

| PCI-1710HGL | 12-bit, 100kS/s High-Gain Multifunction card w/o analog output                               |

| PCI-1711    | 12-bit, 100kS/s 16-ch S.E. Inputs Low-cost Multi-<br>function card                           |

| PCI-1711L   | 12-bit, 100kS/s 16-ch S.E. Inputs Low-cost Multi-<br>function card w/o analog output         |

| PCI-1716    | $16\hbox{-bit}, 250\hbox{kS/s High-Resolution Multifunction card}\\$                         |

| PCI-1716L   | $16\hbox{-bit,}250\hbox{kS/s High-Resolution Multifunction card}\\ \text{w/o analog output}$ |

The following sections of this chapter will provide further information about features of the multifunction cards, a Quick Start for installation, together with some brief information on software and accessories for the PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L card.

# 1.1 Features

| 17 | e Advantech PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/16L provides users with the most requested measurement and ntrol functions as seen below: |  |  |  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|    | PCI-bus mastering for data transfer                                                                                                                 |  |  |  |

|    | 16-channel Single-Ended or 8-channel Differential A/D Input                                                                                         |  |  |  |

|    | 12-bit A/D conversion with up to 100 kHz sampling rate (PCI-1710/1710L/1710HG/1710HGL/1711/1711L)                                                   |  |  |  |

|    | 16-bit A/D conversion with up to $250\mathrm{kHz}$ sampling rate (PCI-1716/1716L)                                                                   |  |  |  |

|    | Programmable gain for each input channel (only for PCI-1710/1710L/1710HGL/1710HGL/1716L)                                                            |  |  |  |

|    | On board samples FIFO buffer:<br>4K for PCI-1710/1710L/1710HG/1710HGL, 1K for PCI-1711/<br>1711L1716/1716L                                          |  |  |  |

|    | 2-channel D/A Output (PCI-1710/1710HG/1711/1716)                                                                                                    |  |  |  |

|    | 16-channel Digital Input                                                                                                                            |  |  |  |

|    | 16-channel Digital Output                                                                                                                           |  |  |  |

|    | Programmable Counter/Timer                                                                                                                          |  |  |  |

|    | Automatic Channel/Gain Scanning                                                                                                                     |  |  |  |

|    | The Advantech PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L offers the following main features:                                               |  |  |  |

# **Plug-and-Play Function**

The Advantech PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L is a Plug-and-Play device, which fully complies with the PCI Specification. Rev 2.1 for PCI-1710/1710L/1710HG/1710HGL/1711/1711L, and Rev 2.2 for PCI-1716/1716L. During card installation, all busrelated configurations such as base I/O address and interrupts are conveniently taken care of by the Plug-and-Play function. You have

virtually no need to set any jumpers or DIP switches.

## Flexible Input Types and Range Settings

The PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L features an automatic channel/gain scanning circuit. This circuit design controls multiplexer switching during sampling. Users can set different gain values for each channel according to their needs for the corresponding range of input voltage. The gain value settings thus selected is stored in the SRAM. This flexible design enables multi-channel and high-speed sampling for high-performance data acquisition.

## On-board FIFO (First-In-First-Out) Memory

The PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L provides an on-board FIFO memory buffer, storing up 1 to 1K/4K A/D samples. Users can either enable or disable the interrupt request feature of the FIFO buffer. While the interrupt request for FIFO is enabled, users are allowed to specify whether an interrupt request will be sent with each sampling action or only when the FIFO buffer is half saturated. This useful feature enables a continuous high-speed data transfer with a more predictable performance on operating systems.

## **Optional D/A Output for Cost Savings**

The PCI-1710/1710HG/1711/1716 goes further with 2 analog output channels, while the PCI-1710L/1710HGL/1711L/1716L doesn't. It is for users to differentiate between the PCI-1710/1710HG/1711/1716 and the PCI-1710L/1710HGL/1711L/1716L according to what they really need as the best solution with no extra cost.

# 16 Digital Inputs and 16 Digital Outputs

The PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L provides 16 digital input channels and 16 digital output channels. Users are left with great flexibility to design and customize their applications according to their specific needs.

# On-board Programmable Counter

The PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L is equipped with a programmable counter, which can serve as a pacer trigger for A/D conversions. The counter chip is an 82C54 or its equivalent, which incorporates three 16-bit counters on a 10 MHz clock. One of the three counters is used as an event counter for input

channels or pulse generation. The other two are cascaded into a 32-bit timer for pacer triggering.

#### Note:

- ▶ Pace trigger determines how fast A/D conversion will be done in pacer trigger mode.

- ➤ For detailed specifications of the PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L, please refer to *Appendix A*, *Specifications*.

# 1.2 Installation Guide

Before you install your PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716L card, please make sure you have the following necessary components:

| co                                                                        | mponents:                                                                      |                                                                                       |  |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|

|                                                                           | PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L<br>Multifunction card      |                                                                                       |  |

|                                                                           | PCI-1710/1710L/17<br>User's Manual                                             | 710HG/1710HGL/1711/1711L/1716/1716L                                                   |  |

|                                                                           | Driver software                                                                | Advantech DLL drivers (included in the companion CD-ROM)                              |  |

|                                                                           | Wiring cable                                                                   | PCL-10168                                                                             |  |

|                                                                           | Wiring board                                                                   | PCLD-8710, ADAM-3968                                                                  |  |

|                                                                           | Computer                                                                       | Personal computer or workstation with a PCI-bus slot (running Windows 95/98/NT/ 2000) |  |

| Some other optional components are also available for enhanced operation: |                                                                                |                                                                                       |  |

|                                                                           | Application software ActiveDAQ, GeniDAQ or other third-party software packages |                                                                                       |  |

| After you get the necessary components and maybe some of the              |                                                                                |                                                                                       |  |

After you get the necessary components and maybe some of the accessories for enhanced operation of your Multifunction card, you can then begin the Installation procedures. Figure 1-1 on the next page provides a concise flow chart to give users a broad picture of the software and hardware installation procedures:

Figure 1-1: Installation Flow Chart

# 1.3 Software

Advantech offers a rich set of DLL drivers, third-party driver support and application software to help fully exploit the functions of your PCI-1710/1710I/1710HG/1710HGL/1711/1711I/1716/1716L.card:

- DLL driver (on the companion CD-ROM)

- LabVIEW driver

- Advantech ActiveDAO

- Advantech GeniDAQ

For more information on software, please refer to *Chapter 4, Software Overview*.

Users who intend to program directly at the registers of the Multifunction card can have register-level programming as an option. Since register-level programming is often difficult and laborious, it is usually recommended only for experienced programmers. For more information, please refer to *Appendix C, Register Structure and Format*.

## 1.4 Accessories

Advantech offers a complete set of accessory products to support the PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L cards. These accessories include:

# Wiring Cable

☐ PCL-10168

The PCL-10168 shielded cable is specially designed for PCI-1710/1710L/1710HG/1710HGL/1711/1711L/ 1716/1716L cards to provide high resistance to noise. To achieve a better signal quality, the signal wires are twisted in such a way as to form a "twisted-pair cable", reducing cross-talk and noise from other signal sources. Furthermore, its analog and digital lines are separately sheathed and shielded to neutralize EMI/EMC problems.

# **Wiring Boards**

☐ ADAM-3968 The ADAM-3968 is a 68-pin SCSI wiring terminal module for DIN-rail mounting. This terminal module

can be readily connected to the Advantech PC-Lab cards and allow easy yet reliable access to individual pin connections for the PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L card.

- □ PCLD-8710 The PCLD-8710 is a DIN-rail mounting screw-terminal board to be used with any of the PC-LabCards which have 68-pin SCSI connectors. The PCLD-8710 features the following functions:

- 2 additional 20-pin flat-cable connectors for digital input and output

- Reserved space on the board to meet future needs for signalconditioning circuits (low-pass filter, voltage attenuator and current shunt)

- Industrial-grade screw-clamp terminal blocks for heavy-duty and reliable connections.

Chapter 1

This page is left blank on purpose.

# 2. Installation

This chapter gives users a package item checklist, proper instructions about unpacking and step-by-step procedures for both driver and card installation. Be noted that using PCI-1716/1716L for example.

# 2.1 Unpacking

After receiving your PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L package, please inspect its contents first. The package should contain the following items:

- ☑ PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L card

- ☑ Companion CD-ROM (DLL driver included)

- ☑ User's Manual

- Quick Start

The PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L card harbors certain electronic components vulnerable to electrostatic discharge (ESD). ESD could easily damage the integrated circuits and certain components if preventive measures are not carefully paid attention to. Before removing the card from the antistatic plastic bag, you should take following precautions to ward off possible ESD damage:

- Touch the metal part of your computer chassis with your hand to discharge static electricity accumulated on your body. Or one can also use a grounding strap.

- Touch the antistatic bag to a metal part of your computer chassis before opening the bag.

- Take hold of the card only by the metal bracket when removing it out of the bag.

## After taking out the card, first you should:

Inspect the card for any possible signs of external damage (loose or damaged components, etc.). If the card is visibly damaged, please notify our service department or our local sales representative immediately. Avoid installing a damaged card into your system.

# Chapter 2

## Also pay extra caution to the following aspects to ensure proper installation:

Avoid physical contact with materials that could hold static electricity such as plastic, vinyl and Styrofoam.

Whenever you handle the card, grasp it only by its edges. DO NOT TOUCH the exposed metal pins of the connector or the electronic components.

#### Note:

## 2.2 Driver Installation

We recommend you to install the driver before you install the PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L card into your system, since this will guarantee a smooth installation process.

The 32-bit DLL driver Setup program for the PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L card is included on the companion CD-ROM that is shipped with your DAS card package. Please follow the steps below to install the driver software:

- **Step 1:** Insert the companion CD-ROM into your CD-ROM drive.

- **Step 2:** The Setup program will be launched automatically if you have the autoplay function enabled on your system. When the Setup Program is launched, you'll see the following Setup Screen.

#### Note:

■ If the autoplay function is not enabled on your computer, use Windows Explorer or Windows *Run* command to execute SETUP.EXE on the companion CD-ROM.

Figure 2-1: The Setup Screen of Advantech Automation Software

- **Step 3:** Select the *DLL Drivers* option.

- **Step 4:** Select the *Windows 95/98* or *Windows NT* or *Windows 2000* option according to your operating system. Just follow the installation instructions step by step to complete your DLL driver setup.

Figure 2-2: Different options for Driver Setup

For further information on driver-related issues, an online version of DLL Drivers Manual is available by accessing the following path:

Start/Programs/Advantech Driver for 95 and 98 (or for NT/2000)/ Driver Manual

## 2.3 Hardware Installation

#### Note:

Make sure you have installed the driver first before you install the card (please refer to 2.2 *Driver Installation*)

After the DLL driver installation is completed, you can now go on to install the PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L card in any PCI slot on your computer. But it is suggested that you should refer to the computer user manual or related documentations if you have any doubt. Please follow the steps below to install the card on your system.

- **Step 1:** Turn off your computer and unplug the power cord and cables. TURN OFF your computer before installing or removing any components on the computer.

- **Step 2:** Remove the cover of your computer.

- **Step 3:** Remove the slot cover on the back panel of your computer.

- **Step 4:** Touch the metal part on the surface of your computer to neutralize the static electricity that might be on your body.

- Step 5: Insert the 1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L card into a PCI slot. Hold the card only by its edges and carefully align it with the slot. Insert the card firmly into place. Use of excessive force must be avoided, otherwise the card might be damaged.

- **Step 6:** Fasten the bracket of the PCI card on the back panel rail of the computer with screws.

- **Step 7:** Connect appropriate accessories (68-pin cable, wiring terminals, etc. if necessary) to the PCI card.

- **Step 8:** Replace the cover of your computer chassis. Re-connect the cables you removed in step 2.

- **Step 9:** Plug in the power cord and turn on the computer.

#### Note:

No case you installed the card without installing the DLL driver first, Windows 95/98 will recognize your card as an "unknown device" after rebooting, and will prompt you to provide the necessary driver. You should ignore the prompting messages (just click the *Cancel* button) and set up the driver according to the steps described in 2.2 Driver Installation.

After the PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L card is installed, you can verify whether it is properly installed on your system in the *Device Manager*:

- Access the *Device Manager* through Control Panel/System/Device Manager.

- 2. The device name of the PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L should be listed on the *Device Manager* tab on the *System Property* Page.

Figure 2-3: The device name listed on the Device Manager

#### Note:

■ If your card is properly installed, you should see the device name of your card listed on the *Device Manager* tab. If you do see your device name listed on it but marked with an exclamation sign "!", it means your card has not been correctly installed. In this case, remove the card device from the *Device Manager* by selecting its device name and press the *Remove* button. Then go through the driver installation process again.

After your card is properly installed on your system, you can now configure your device using the *Device Installation Program* that has itself already been installed on your system during driver setup. A complete device installation procedure should include device setup, configuration and testing. The following sections will guide you through the *Setup*, *Configuration* and *Testing* of your device.

# 2.4 Device Setup & Configuration

The Device Installation program is a utility that allows you to set up, configure and test your device, and later stores your settings on the system registry. These settings will be used when you call the APIs of Advantech 32-bit DLL drivers.

## **Setting Up the Device**

Step 1: To install the I/O device for your card, you must first run the Device Installation program (by accessing *Start/Programs/Advantech Driver for 95 and 98 (or for NT/2000)/Device Installation*).

Figure 2-4: The Advantech Device Installation utility program

Step 2: On the *Device Installation* program window, select the Setup menu item on the menu bar, and click the *Device* command (Figure 2-4) to bring up the *I/O Device Installation* dialog box (Figure 2-5). You can then view the device(s) already installed on your system (if any) on the *Installed Devices* list box. Since you haven't installed any device yet, you might see a blank list such as the one on the next page (Figure 2-5).

Figure 2-5: The I/O Device Installation dialog box

Step 3: Scroll down the List of Devices box to find the device that you wish to install, then click the *Add*... button to evoke the *Device(s) found* dialog box such as one shown in Figure 2-6. The *Device(s) found* dialog box lists all the installed devices of selected option on your system. Select the device you want to configure from the list box and press the *OK* button. After you have clicked *OK*, you will see a *Device Setting* dialog box such as the one in Figure 2-8.

Figure 2-6: The "Device(s) Found" dialog box

## **Configuring the Device**

**Step 4:** On the *Device Setting* dialog box (Figure 2-7), you can configure the voltage source either as External or Internal, and specify the voltage output range for the 2 D/A channels.

Figure 2-7: The Device Setting dialog box

#### Note:

Now Users can configure the source of D/A reference voltage either as Internal or External, and select the output voltage range. When selecting voltage source as Internal, users have two options for the output voltage range:  $0 \sim 5$  V and  $0 \sim 10$  V.

When selected as External, the output voltage range is determined by the external reference voltage in the following way:

By inputting an external reference voltage: -xV, where  $|x| \le 10$ , you will get a output voltage range: 0 to xV.

**Step 5:** After you have finished configuring the device, click *OK* and the device name will appear in the *Installed Devices* box as seen below:

Figure 2-8: The Device Name appearing on the list of devices box

#### Note:

As we have noted, the device name "000:PCI-1716 I/O=E000H"

begins with a device number "000", which is specifically assigned to

each card. The device number is passed to the driver to specify which

device you wish to control.

If you want to test the card device further, go right to the next section on the *Device Testing*.

# 2.5 Device Testing

Following through the Setup and Configuration procedures to the last step described in the previous section, you can now proceed to test the device by clicking the *Test* Button on the *I/O Device Installation* dialog box (Figure 2-8). A *Device Test* dialog box will appear accordingly:

Figure 2-9: Analog Input tab on the Device Test dialog box

On the *Device Test* dialog box, users are free to test various functions of PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L on the *Analog output, Digital input, Digital output* or *Counter tabs*. And the *Analog output* function only available for 1710/1710HG/1711/1716.

#### Note:

- Nou can access the Device Test dialog box either by the previous procedure for the Device Installation Program or simply by accessing Start/Programs/Advantech Driver for 95 and 98 (or for NT/2000) / Test Utility.

- All the functions are performed by software polling method. For highspeed data acquirement or output, they have to use corresponding VC example like ADINT or ADDMA or ADBMDMA.

## **Testing Analog Input Function**

Click the *Analog Input* tab to bring it up to the front of the screen. Select the input range for each channel in the Input range drop-down boxes. Configure the sampling rate on the scroll bar. Switch the channels by using the up/down arrow.

Figure 2-10: Analog Input tab on the Device Test dialog box

# Testing Analog Output Function (only for PCI-1710/1710HG/1711/1716)

Click the *Analog Output* tab to bring it up to the foreground. The *Analog Output* tab allows you to output quasi-sine, triangle, or square waveforms generated by the software automatically, or output single values manually. You can also configure the waveform frequency and output voltage range.

Figure 2-11: Analog Output tab on the Device Test dialog box

# **Testing Digital Input Function**

Click the *Digital Input* tab to show forth the *Digital Input* test panel as seen below. Through the color of the lamps, users can easily discern whether the status of each digital input channel is either high or low.

Figure 2-12: Digital Input tab on the Device Test dialog box

## **Testing Digital Output Function**

Click the *Digital Output* tab to bring up the *Digital Output* test panel such as the one seen on the next page. By pressing the buttons on each tab, users can easily set each digital output channel as *high* or *low* for the corresponding port.

Figure 2-13: Digital Output tab on the Device Test dialog box

## **Testing Counter Function**

Click the *Counter* Tab to bring its test panel forth. The counter channel (Channel 0) offers the users two options: Event counting and Pulse out. If you select Event counting, you need first to connect your clock source to pin CNT0\_CLK, and the counter will start counting after the pin CNT0\_GATE is triggered. If you select Pulse Out, the clock source will be output to pin CNT0\_OUT. You can configure the Pulse Frequency by the scroll bar right below it.

Figure 2-14: Counter tab on the Device Test dialog box

Only after your card device is properly set up, configured and tested, can the device installation procedure be counted as complete. After the device installation procedure is completed, you can safely proceed to the next chapter, *Signal Connections*.

# 3. Signal Connections

### 3.1 Overview

Maintaining signal connections is one of the most important factors in ensuring that your application system is sending and receiving data correctly. A good signal connection can avoid unnecessary and costly damage to your PC and other hardware devices. This chapter provides useful information about how to connect input and output signals to the PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L via the I/O connector.

## 3.2 I/O Connector

The I/O connector on the PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L is a 68-pin connector that enable you to connect to accessories with the PCL-10168 shielded cable.

#### Note:

➤ The PCL-10168 shielded cable is especially designed for the PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L to reduce noise in the analog signal lines. Please refer to Section 1.4 Accessories.

# **Pin Assignment**

Figure 3-1 shows the pin assignments for the 68-pin I/O connector on the PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L.

#### Note:

Note three ground references AIGND, AOGND, and DGND should be used discreetly each according to its designated purpose. Actually, we offer the individual GND pin for AI, AO and DIO to provide best signal quality. However, all the signals on the DA&C card need to refer to the same GND finally. So we test and choice a best point to connect AIGND, AOGND and DGND together. In short, this is base on the "single-point" ground principle.

| AI0       | 68 | 34     | Al1       |

|-----------|----|--------|-----------|

| Al2       | 67 | 33     | AI3       |

| Al4       | 66 | 32     | AI5       |

| Al6       | 65 | 31     | AI7       |

| AI8       | 64 | 30     | AI9       |

| AI10      | 63 | 29     | AI11      |

| Al12      | 62 | 28     | AI13      |

| Al14      | 61 | 27     | AI15      |

| AIGND     | 60 | 26     | AIGND     |

| AO0_REF*  | 59 | 25     | AO1_REF*  |

| AO0_OUT*  | 58 | 24     | AO1_OUT*  |

| AOGND*    | 57 | 23     | AOGND*    |

| DI0       | 56 | 22     | DI1       |

| DI2       | 55 | 21     | DI3       |

| DI4       | 54 | 20     | DI5       |

| DI6       | 53 | 19     | DI7       |

| DI8       | 52 | 18     | DI9       |

| DI10      | 51 | 17     | DI11      |

| DI12      | 50 | 16     | DI13      |

| DI14      | 49 | 15     | DI15      |

| DGND      | 48 | 14     | DGND      |

| DO0       | 47 | 13     | DO1       |

| DO2       | 46 | 12     | DO3       |

| DO4       | 45 | 11     | DO5       |

| DO6       | 44 | 10     | DO7       |

| DO8       | 43 | 9      | DO9       |

| DO10      | 42 | 8      | DO11      |

| DO12      | 41 | 7      | DO13      |

| DO14      | 40 | 6      | DO15      |

| DGND      | 39 | 5      | DGND      |

| CNT0_CLK  | 38 | 4      | PACER_OUT |

| CNT0_OUT  | 37 | 3      | TRG_GATE  |

| CNT0_GATE | 36 | 2      | EXT_TRG   |

| +12V      | 35 | 1      | +5V       |

|           |    |        |           |

|           |    |        |           |

|           |    | $\sim$ |           |

Figure 3-1: I/O connector pin assignments for the PCI-1710/1710L/ 1710HG/1710HGL/1711/1711L/1716/1716L

<sup>\*:</sup> Pins 23~25 and pins 57~59 are not defined for PCI-1710L/1710HGL/ 1711L/1716L

# I/O Connector Signal Description

Table 3-1: I/O Connector Signal Description

| Cianal Nari        | Deference- | Direction | Description                                                                                                                                                                                                                                                             |

|--------------------|------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name        | Reference  | Direction | Description                                                                                                                                                                                                                                                             |

| AI<015>            | AIGND      | Input     | Analog Input Channels 0 through 15. Each channel pair, Al <i, i+1=""> (i = 0, 2, 414), can be configured as either two single-ended inputs or one differential input of PCI-1710/1710L/1710HG/1710HGL/1716/1716L.</i,>                                                  |

| AIGND              | -          | -         | Analog Input Ground. The three ground references (AIGND, AOGND, and DGND) are connected together on the PCI-1710/1710L/1710HGL/1711/H711L/1716L card.                                                                                                                   |

| A00_REF<br>A01_REF | AOGND      | Input     | Analog Output Channel 0/1 External Reference.                                                                                                                                                                                                                           |

| A00_0UT<br>A01_0UT | AOGND      | Output    | Analog Output Channels 0/1.                                                                                                                                                                                                                                             |

| AOGND              | 1          | -         | Analog Output Ground. The analog output voltages are referenced to these nodes. The three ground references (AIGND, AOGND, and DGND) are connected together on the PCI-1710/1710L/1710HGL/1710HGL/1711/1711L/1716/1716L card.                                           |

| DI<015>            | DGND       | Input     | Digital Input channels.                                                                                                                                                                                                                                                 |

| D0<015>            | DGND       | Output    | Digital Output channels.                                                                                                                                                                                                                                                |

| DGND               | -          | -         | Digital Ground. This pin supplies the reference for the digital channels at the I/O connector as well as the +5VDC supply. The three ground references (AIGND, AOGND, and DGND) are connected together on the PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L card. |

| CNTO_CLK           | DGND       | Input     | Counter 0 Clock Input. The clock input of counter 0 can be either external or internal , as set by software.                                                                                                                                                            |

| CNTO_OUT           | DGND       | Output    | Counter 0 Output.                                                                                                                                                                                                                                                       |

| CNTO_GATE          | DGND       | Input     | Counter 0 Gate Control.                                                                                                                                                                                                                                                 |

| PACER_OUT          | DGND       | Output    | Pacer Clock Output. This pin pulses once for each pacer clock when turned on. If A/D conversion is in the pacer trigger mode, users can use this signal as a synchronous signal for other applications. A low- to- high edge triggers A/D conversion to start.          |

| TRG_GATE           | DGND       | Input     | A/D External Trigger Gate. When TRG _GATE is connected to +5 V, it will enable the external trigger signal to input. When TRG _GATE is connected to DGND, it will disable the external trigger signal to input.                                                         |

| EXT_TRG            | DGND       | Input     | A/D External Trigger. This pin is external trigger signal input for the A/D conversion. A low-to-high edge triggers A/D conversion to start.                                                                                                                            |

| +12V               | DGND       | Output    | +12 VDC Source.                                                                                                                                                                                                                                                         |

| +5V                | DGND       | Output    | +5 VDC Source.                                                                                                                                                                                                                                                          |

# 3.3 Analog Input Connections

The PCI-1710/1710L/1710HG/1710HGL/1716L supports both 16-channel Single-Ended or 8 differential A/D Input, however the PCI-1711/1711L only supports 16 single-ended analog inputs. Each individual input channel is software-selected.

## Single-ended Channel Connections

The single-ended input configuration has only one signal wire for each channel, and the measured voltage  $(V_m)$  is the voltage of the wire as referenced against the common ground.

A signal source without a local ground is also called a "floating source". It is fairly simple to connect a single-ended channel to a floating signal source. In this mode, the PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L provides a reference ground for external floating signal sources. Figure 3-2 shows a single-ended channel connection between a floating signal source and an input channel on the PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L.

Figure 3-2: Single-ended input channel connection

### **Differential Channel Connections**

The differential input channels operate with two signal wires for each channel, and the voltage difference between both signal wires is measured. On the PCI-1710/1710L/1710HG/1710HGL/1716/1716L, when all channels are configured to differential input, up to 8 analog channels are available.

If one side of the signal source is connected to a local ground, the signal source is ground-referenced. Therefore, the ground of the signal source and the ground of the card will not be exactly of the same voltage. The difference between the ground voltages forms a common-mode voltage ( $V_{\text{cm}}$ ).

To avoid the ground loop noise effect caused by common-mode voltages, you can connect the signal ground to the Low input. Figure 3-3 shows a differential channel connection between a ground-reference signal source and an input channel on the PCI-1710/1710L/1710HGL/1716/1716L. With this connection, the PGIA rejects a common-mode voltage  $V_{\rm cm}$  between the signal source and the PCI-1710/1710L/1710HG/1710HGL/1716/1716L ground, shown as  $V_{\rm cm}$  in Figure 3-3.

Figure 3-3: Differential input channel connection - ground reference signal source

If a floating signal source is connected to the differential input channel, the signal source might exceed the common-mode signal range of the PGIA, and the PGIA will be saturated with erroneous voltage-readings. You must therefore reference the signal source against the AIGND.

Figure 3-4 shows a differential channel connection between a floating signal source and an input channel on the PCI-1710/1710L/1710HG/1710HGL/1716/1716L. In this figure, each side of the floating signal source is connected through a resistor to the AIGND. This connection can reject the common-mode voltage between the signal source and the PCI-1710/1710L/1710HG/1710HGL/1716/1716L ground.

Figure 3-4: Differential input channel connection - floating signal source

However, this connection has the disadvantage of loading the source down with the series combination (sum) of the two resistors. For  $r_a$  and  $r_b$ , for example, if the input impedance  $r_s$  is 1 kW, and each of the two resistors is 100 kW, then the resistors load down the signal source with 200 k $\Omega$  (100 k $\Omega$ + 100 k $\Omega$ ), resulting in a -0.5% gain error. The following gives a simplified representation of the circuit and calculating process.

$$V_{i} = \frac{r_{a} + r_{b}}{r_{s} + r_{a} + r_{b}} \quad V_{s} = \frac{200}{1 + 200} \quad V_{s} = \frac{200}{201} \quad V_{s}$$

$$V_{i} = \frac{r_{a} + r_{b}}{r_{s} + r_{a} + r_{b}} \quad V_{s} = \frac{200}{1 + 200} \quad V_{s} = \frac{200}{201} \quad V_{s}$$

$$V_{i} = \frac{V_{i} - V_{s}}{V_{s} + V_{s} + V_{s}} = -\frac{1}{201} = -0.5\%$$

# 3.4 Analog Output Connections

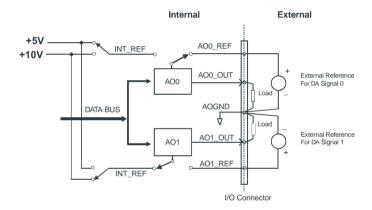

The PCI-1710/1710HG/1711/1716 provides two D/A output channels (PCI-1710L/1710HGL/1711L/1716L are not designed to have this function), AO0\_OUT and AO1\_OUT. Users may use the PCI-1710/1710HG/1711/1716 internally-provided precision -5V (-10V) reference to generate 0 to +5 V (+10 V) D/A output range. Users also may create D/A output range through external references, AO0\_REF and AO1\_REF. The external reference input range is +/-10 V. For example, connecting with an external reference of -7 V will generate 0 ~ +7 V D/A output.

Figure 3-5 shows how to make analog output and external reference input connections on the PCI-1710/1710HG/1711/1716.

Figure 3-5: Analog output connections

# 3.5 Trigger Source Connections

#### **Internal Pacer Trigger Connection**

The PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L includes one 82C54 compatible programmable Timer/Counter chip which provides three 16-bit counters connected to a Oscillator, each designated specifically as Counter 0, Counter 1 and Counter 2. Counter 0 is a counter which counts events from an input channel or outputing pulse. Counter 1 and Counter 2 are cascaded to create a 32-bit timer for pacer triggering. A low-to-high edge from the Counter 2 output (PACER\_OUT) will trigger an A/D conversion on the PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L. At the same time, you can also use this signal as a synchronous signal for other applications.

#### **External Trigger Source Connection**

In addition to pacer triggering, the PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L also allows external triggering for A/D conversions. When a +5 V source is connected to TRG\_GATE, the external trigger function is enabled. A low-to-high edge coming from EXT\_TRG will trigger an A/D conversion on the PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L. When DGND is connected to TRG\_GATE, the external trigger function is thereby disabled.

# 3.6 Field Wiring Considerations

When you use the PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L to acquire data from outside, noises in the environment might significantly affect the accuracy of your measurements if due cautions are not taken. The following measures will be helpful to reduce possible interference running signal wires between signal sources and the PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L.

- The signal cables must be kept away from strong electromag-netic sources such as power lines, large electric motors, circuit breakers or welding machines, since they may cause strong electromagnetic interference. Keep the analog signal cables away from any video monitor, since it can significantly affect a data acquisition system.

- If the cable travels through an area with significant electromagnetic

interference, you should adopt individually shielded, twisted-pair

wires as the analog input cable. This type of cable has its signal

wires twisted together and shielded with a metal mesh. The metal

mesh should only be connected to one point at the signal source

ground.

- Avoid running the signal cables through any conduit that might have power lines in it.

- If you have to place your signal cable parallel to a power line that

has a high voltage or high current running through it, try to keep a

safe distance between them. Or, you should place the signal cable

at a right angle to the power line to minimize the undesirable effect.

- The signals transmitted on the cable will be directly affected by the quality of the cable. In order to ensure better signal quality, we recommend that you use the PCL-10168 shielded cable.

Chapter 3

This page is left blank on purpose.

# 4. Software Overview

This chapter gives you an overview of the software programming choices available and a quick reference to source codes examples that can help you be better oriented to programming. After following the instructions given in *Chapter 2*, it is hoped that you feel comfortable enough to proceed further.

Programming choices for DAS cards: You may use Advantech application software such as Advantech DLL driver. On the other hand, advanced users are allowed another option for register-level programming, although not recommended due to its laborious and time-consuming nature.

# 4.1 Programming Choices

#### **DLL Driver**

The Advantech DLL Drivers software is included on the companion CD-ROM at no extra charge. It also comes with all the Advantech DAS cards. Advantech's DLL driver features a complete I/O function library to help boost your application performance. The Advantech DLL driver for Windows 95/98/NT/2000 works seamlessly with development tools such as Visual C++, Visual Basic, Inprise C++ Builder and Inprise Delphi.

# Register-level Programming

Register-level programming is reserved for experienced programmers who find it necessary to write codes directly at the level of device registers. Since register-level programming requires much effort and time, we recommend that you use the Advantech DLL drivers instead. However, if register-level programming is indispensible, you should refer to the relevant information in *Appendix C, Register Structure and Format*, or to the example codes included on the companion CD-ROM.

# 4.2 DLL Driver Programming Roadmap

This section will provide you a roadmap to demonstrate how to build an application from scratch using Advantech DLL driver with your favorite development tools such as Visual C++, Visual Basic, Delphi and C++ Builder. The step-by-step instructions on how to build your own applications using each development tool will be given in the DLL Drivers Manual. Moreover, a rich set of example source codes are also given for your reference.

#### **Programming Tools**

| Programmers can develop application programs with their favorite development tools: |

|-------------------------------------------------------------------------------------|

| ☐ Visual C++                                                                        |

| ☐ Visual Basic                                                                      |

| □ Delphi                                                                            |

| ☐ C++ Builder                                                                       |

| For instructions on how to begin programming works in each devel                    |

For instructions on how to begin programming works in each development tool, Advantech offers a *Tutorial* Chapter in the *DLL Drivers Manual* for your reference. Please refer to the corresponding sections in this chapter on the *DLL Drivers Manual* to begin your programming efforts. You can also take a look at the example source codes provided for each programming tool, since they can get you very well-oriented.

The *DLL Drivers Manual* can be found on the companion CD-ROM. Or if you have already installed the DLL Drivers on your system, The *DLL Drivers Manual* can be readily accessed through the *Start* button:

# Start/Programs/Advantech Driver for 95 and 98 (or for NT/2000)/Driver Manual

The example source codes could be found under the corresponding installation folder such as the default installation path:

### \Program Files\Advantech\ADSAPI\Examples

For information about using other function groups or other development tools, please refer to the *Creating Windows 95/NT/2000 Application with DLL Driver* chapter and the *Function Overview* chapter on the *DLL Drivers Manual*.

### **Programming with DLL Driver Function Library**

Advanech DLL driver offers a rich function library to be utilized in various application programs. This function library consists of numerous APIs that support many development tools, such as Visual C++, Visual Basic, Delphi and C++ Builder.

According to their specific functions or sevices, those APIs can be categorized into several function groups:

| Analog Iutput Function Group           |

|----------------------------------------|

| Analog Output Function Group           |

| Digital Input/Output Function Group    |

| Counter Function Group                 |

| Temperature Measurement Function Group |

| Alarm Function Group                   |

| Port Function Group                    |

| Communication Function Group           |

| <b>Event Function Group</b>            |

For the usage and parameters of each function, please refer to the Function Overview chapter in the DLL Drivers Manaul.

# **Troubleshooting DLL Driver Error**

Driver functions will return a status code when they are called to perform a certain task for the application. When a function returns a code that is not zero, it means the function has failed to perform its designated function. To troubleshoot the DLL driver error, you can pass the error code to **DRV\_GetErrorMessage** function to return the error message. Or you can refer to the DLL Driver Error Codes Appendix in the DLL Drivers Manaul for a detailed listing of the Error Code, Error ID and the Error Message.

Chapter 4

This page is left blank on purpose.

# 5. Calibration

This chapter provides brief information on PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L calibration. Regular calibration checks are important to maintain accuracy in data acquisition and control applications. We provide the calibration programs or utility on the companion CD-ROM to assist you in A/D and D/A calibration.

#### Note:

If you installed the program to another directory, you can find these programs in the corresponding subfolders in your destination directory.

The PCI-1710/1710L/1710HG/1710HGL/1711/1711L/1716/1716L has been calibrated at the factory for initial use. However, a calibration of the analog input and the analog output function every six months is recommended.

These calibration programs make calibration an easy job. With a variety of prompts and graphic displays, these programs will lead you through the calibration and setup procedures, showing you all the correct settings and adjustments.

To perform a satisfactory calibration, you will need a 4½-digit digital multi-meter and a voltage calibrator or a stable, noise-free D. C. voltage source.

#### Note:

▶ Before you calibrate the A/D or D/A function, you must turn on the power at least **15 minutes** to make sure the DAS card getting stable.

### 5.1 PCI-1710/1710L/1710HG/1710HGL Calibration

Two calibration programs are included on the companion CD-ROM:

ADCALEXE A/D calibration program

**DACALEXE D/A calibration program** (only for PCI-1710/1710HG)

These calibration programs are designed only for the DOS environment. Access these programs from the default location:

C:\Program Files\Advantech\ADSAPI\Utility\PCI1710

### **VR Assignment**

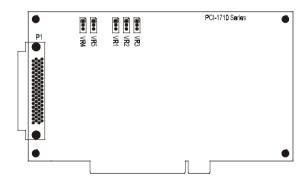

There are five variable resistors (VRs) on the PCI-1710/1710HG card and three variable resistors (VRs) on the PCI-1710L/1710HGL card. These variable resistors are to facilitate accurate adjustments for all A/D and D/A channels. Please refer to the following two figures for the VR positions.

Figure 5-1: PCI-1710/1710L/1710HG/1710HGL VR assignment

The following list shows the function of each VR:

| VR  | Function                                                          |  |  |  |

|-----|-------------------------------------------------------------------|--|--|--|

| VR1 | A/D unipolar offset adjustment                                    |  |  |  |

| VR2 | A/D bipolar offset adjustment                                     |  |  |  |

| VR3 | A/D full scale (gain) adjustment                                  |  |  |  |

| VR4 | D/A channel 0 full scale adjustment<br>(for PCI-1710/1710HG only) |  |  |  |

| VR5 | D/A channel 1 full scale adjustment<br>(for PCI-1710/1710HG only) |  |  |  |

#### A/D Calibration

Regular and accurate calibration procedures ensure the maximum possible accuracy. The ADCAL.EXE calibration program leads you through the whole A/D offset and gain adjustment procedure. The basic steps are outlined below:

- 1. Set analog input channel AI0 as single-ended, bipolar, range  $\pm 5$  V, and set AI1 as single-ended, unipolar, range 0 to 10 V.

- 2. Connect a DC voltage source with value equal to 0.5 LSB (-4.9959) V) to AI0.

- 3. Adjust VR2 until the output codes from the card's AI0 flickers between 0 and 1.

- 4. Connect a DC voltage source with a value of 4094.5 LSB (4.9953 V) to AIO.

- 5. Adjust VR3 until the output codes from the card's AI0 flickers between 4094 and 4095.

- 6. Repeat step 2 to step 5, adjusting VR2 and VR3.

- 7. Connect a DC voltage source with value equal to 0.5 LSB (1.22 mV) to AI1.

- 8. Adjust VR1 until the output codes from the card's AI1 flickers between 0 and 1.

| A/D  | code | Mapping     | Voltage           |

|------|------|-------------|-------------------|

| Hex. | Dec. | Bipolar ±5V | Unipolar 0 to 10V |

| 000h | 0    | -4.9971 V   | 0 V               |

| 7FFh | 2047 | -0.0024 V   | 4.9947 V          |

| 800h | 2048 | 0 V         | 4.9971 V          |

| FFFh | 4095 | 4.9947 V    | 9.9918 V          |

### D/A Calibration (for PCI-1710/1710HG only)

In a way similar to the ADCAL.EXE program, the DACAL.EXE program leads you through the whole D/A calibration procedure.

You can either use the on-board -5 V (-10 V) internal reference voltage or use an external reference. If you use an external reference, connect a reference voltage within the range  $\pm 10$  V to the reference input of the D/A output channel you want to calibrate. Adjust the full scale (gain) of D/A channel 0 and 1, with VR4 and VR5 respectively.

#### Note:

Using a precision voltmeter to calibrate the D/A outputs is recommended.

Set the D/A data register to 4095 and adjust VR3 until the D/A output voltage equals the reference voltage minus 1 LSB, but with the opposite sign. For example, if V ref is -5 V, then V out should be +4.9959 V. If V ref is -10 V, V out should be +9.9918 V.

#### Self A/D Calibration

Under many conditions, it is difficult to find a good enough DC voltage source for A/D calibration. There is a simple method to solve this problem. First, you should calibrate D/A channel 0, DA0\_OUT, with internal reference -5 V, and D/A channel 1, DA1\_OUT, with reference -10 V.

Then, run the ADCAL.EXE program to finish the self-A/D calibration procedure.

- 1. Set AI0 as differential, bipolar, range  $\pm 5$  V and AI2 as differential, unipolar, range 0 to 10 V.

- 2. Connect DA0\_OUT with codes equal to 4095 LSB (4.9959 V) to AI 0. Notice that the polarity of AI0 should be connected with reverse polarity (i.e. D/A + to A/D -, D/A to A/D +).

- 3. Adjust VR2 until the output codes from the card's AI0 flicker between 0 and 1.

- 4. Connect DA0\_OUT with codes equal to 4095 LSB (4.9959 V) to AI0.

- 5. Adjust VR3 until the output codes from the card's AI0 flickers between 4094 and 4095.

- 6. Repeat steps 2 through 5, adjusting VR2 and VR3.

- 7. Connect DA1\_OUT with codes equal to 1 LSB (2.44 mV) to AI2.

- 8. Adjust VR1 until the output codes from the card's AI1 flicker between 0 and 1.

- Finish ADCAL, EXE.

#### 5.2 PCI-1711/1711L Calibration

Three calibration programs are included on the companion CD-ROM:

ADCALEXE A/D calibration program

**DACALEXE D/A calibration program** (only for PCI-1711)

**SELFCALEXE D/A self-calibration program** (only for PCI-1711)

These calibration programs are designed only for the DOS environment. Access these programs from the default location:

C:\Program Files\Advantech\ADSAPI\Utility\PCI1711

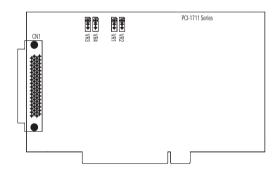

### **VR Assignment**

There are four variable resistors (VRs) on the PCI-1711 card and two variable resistors (VRs) on the PCI-1711L card. These variable resistors are to facilitate accurate adjustments for all A/D and D/A channels. Please refer to the following figure for the VR positions.

Figure 5-2: PCI-1711/1711L VR assignment

The following list shows the function of each VR:

| VR  | Function                                                   |  |  |  |

|-----|------------------------------------------------------------|--|--|--|

| VR1 | A/D bipolar offset adjustment                              |  |  |  |

| VR2 | A/D full scale (gain) adjustment                           |  |  |  |

| VR3 | D/A channel 0 full scale adjustment<br>(for PCI-1711 only) |  |  |  |

| VR4 | D/A channel 1 full scale adjustment<br>(for PCI-1711 only) |  |  |  |

#### A/D Calibration

Regular and accurate calibration procedures ensure the maximum possible accuracy. The A/D calibration program ADCAL.EXE leads you through the whole A/D offset and gain adjustment procedure. The basic steps are outlined below:

- 1. Connect a DC voltage source of +9.995 V to AIO.

- 2. Connect AGND to AI1, AI2, AI3, AI4 and AI5.

- 3. Run the ADCAL.EXE program.

- 4. Adjust VR2 until the output codes from the card's AI0 are focused on FFE (at least 70%), and adjust VR1 until the output codes from the card's AI1, AI2, AI3, AI4 and AI5 are focused on 7FF (at least 70%).

- 5. Press the SPACE key to finish A/D calibration.

#### D/A Calibration (for PCI-1711 only)

The D/A calibration program DACAL.EXE leads you through the whole D/A calibration procedure.

You can select the on-board -5V or -10V internal reference voltage or an external voltage as your analog output reference voltage. If you use an external reference, connect a reference voltage within the range of  $\pm 10 V$  to the reference input of the D/A output channel you want to calibrate. Adjust the full scale of D/A channel 0 and 1, with VR3 and VR4 respectively.

#### Note:

Using a precision voltmeter to calibrate the D/A outputs is recommended.

You can adjust VR3 and VR4 until the D/A channel 0 and 1 output voltages approach the reference voltage (at least 1LSB), but with the reverse sign. For example, if Vref is -5V, then Vout should be +5V. If Vref is -10V, Vout should be +10V.

#### Self A/D Calibration

We know, in most cases, it is difficult to find a good enough DC voltage source for A/D calibration. We provide a self-adjusted A/D calibration program "SELFCAL.EXE" to help solve this problem. The steps of self-calibration are outlined as below:

- 1. Connect DA0\_OUT to AI0.

- 2. Connect AGND to AI1, AI2, AI3, AI4 and AI5.

- 3. Run the SELFCAL.EXE program.

- 4. First calibrate the D/A channel. Adjust VR3 until the DA0\_OUT output voltage approaches +10V. Then press the SPACE key.

- 5. Next we will do the A/D calibration. Now the DA0\_OUT output voltage will be +9.995V, then adjust VR2 until the output codes from the card's AI0 focused on FFE (at least 70%) and adjust VR1 until the output codes from the card's AI1, AI2, AI3, AI4 and AI5 focused on 7FF (at least 70%).

- 6. Press the SPACE key to finish calibration procedures.

### 5.3 PCI-1716/1716L Calibration

A calibration utility, AutoCali, is included on the companion CD-ROM:

**AutoCali.EXE** PCI-1716/1716L calibration utility

This calibration utility is designed for the Microsoft©Windows<sup>TM</sup> environment. Access this program from the default location:

C:\Program Files\Advantech\ADSAPI\Utility\Auto Calibration

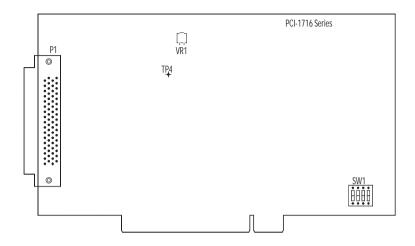

# **VR** Assignment

There is one variable resistor (VR1) on the PCI-1716/1716L to adjust the accurate reference voltage on the PCI-1716/1716L. We have provided a test point (See TP4 in Figure 5-3) for you to check the reference voltage on board. Before you start to calibrate A/D and D/A channels, please adjust VR1 until the reference voltage on TP4 has reached +5.0000 V. Figure 5-3 shows the locations of VR1 and TP4.

Figure 5-3: PCI-1716/1716L VR assignment

### **Calibration Utility**

The calibration utility, AutoCali, provides four functions - auto A/D calibration, auto D/A calibration, manual A/D calibration and manual D/A calibration. The program helps the user to easily finish the calibration procedures automatically; however, the user can calibrate the PCI-1716/1716L manually. *Appendix E* illustrated the standard calibration procedures for your reference. If you want to calibrate the hardware in your own way, these two sections will guide you. The following steps will guide you through the PCI-1716/1716L software calibration.

**Step 1:** Access the calibration utility program *AutoCali*.exe from the default location:

C:\Program Files\Advantech\ADSAPI\Utility\Auto Calibration

#### Note:

► If you installed the program to another directory, you can find this program in the corresponding subfolders in your destination directory.

**Step 2:** Select PCI-1716/1716L in the ADSDAQ dialog box.

Figure 5-4: Selecting the device you want to calibrate

**Step 3:** After you start to calibrate the PCI-1716/1716L, please don't forget to adjust VR1.

Figure 5-5: Warning message before start calibration

#### A/D channel Auto-Calibration

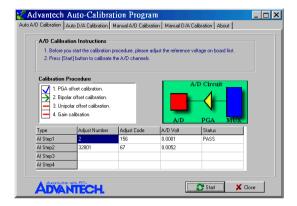

**Step 4:** Click the *Auto A/D Calibration* tab to show the A/D channel auto-calibration panel (Fig. 5-6). Press the start button to calibrate A/D channels automatically.

Figure 5-6: Auto A/D Calibration Dialog Box

**Step 5:** The first A/D calibration procedure is enabled (Fig. 5-7).

Figure 5-7: A/D Calibration Procedure 1

**Step 6:** The second A/D calibration procedure is enabled (Fig. 5-8)

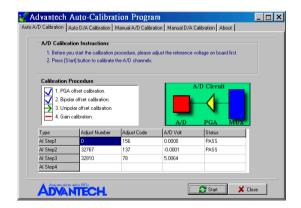

Figure 5-8: A/D Calibration Procedure 2

**Step 7:** The third A/D calibration procedure is enabled (Fig. 5-9)

Figure 5-9: A/D Calibration Procedure 3

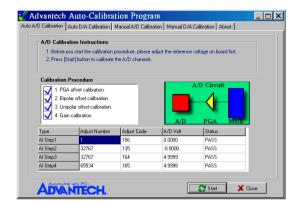

**Step 8:** Auto-calibration is finished. (See fig. 5-10)

Figure 5-10: A/D Calibration is finished

#### D/A channel Auto-Calibration

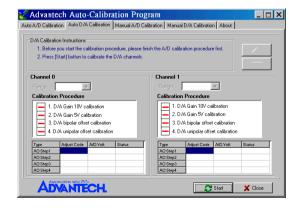

**Step 9:** Click the *Auto D/A Calibration* tab to show the D/A channel auto calibration panel. Please finish the A/D calibration procedure first before you start the D/A calibration procedure. There are two D/A channels in PCI-1716; select the output range for each channel and then press the start button to calibrate D/A channels (Fig. 5-11).

Figure 5-11: Range Selection in D/A Calibration

**Step 10:** D/A channel 0 calibration is enabled (Fig. 5-12)

Figure 5-12: Calibrating D/A Channel 0

**Step 11:** D/A channel 1 calibration is enabled (Fig. 5-13)

Figure 5-13: Calibrating D/A Channel 1

**Step 12:** Auto-calibration is finished (Fig. 5-14)

Figure 5-14: D/A Calibration is finished

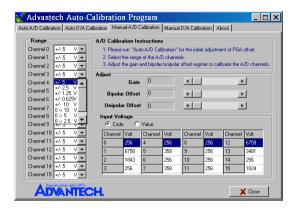

#### A/D channel Manual-Calibration

**Step 1:** Click the *Manual A/D Calibration* tab to show the A/D channel manual calibration panel. Before calibrating, acquire the reference voltage from a precision standard voltage reference. Go to the *Range* form, select a channel and the target voltage range according to the input voltage value from a precision standard voltage reference(Fig. 5-15).

#### Note:

- No. The input voltage value you selected from a precision standard voltage reference needs to correspond with the one that the PCI-1716/1716L can read.

- No The input voltage will be analog code so the computer will convert the voltage data into digitial code; therefore, the input voltage value you selected from a precision standard voltage reference needs to correspond with the one that the PCI-1716/1716L can read. For example, if the input range is 0 ∼ 5V, then input voltage should be 2.9992V not 3V.

Figure 5-15: Selecting Input Rage in Manual A/D Calibration panel

**Step 2:** According to the difference between reference voltage and receiving data in PCI-1716/1716L, adjust the gain, bipolar offset and unipolar offset registers (Figure 5-16)

Figure 5-16: Adjusting registers

**Step 3:** Adjust the registers until they fall between the input voltage from the standard voltage reference and the receiving voltage reflectected in the *Manual A/D Calibration* tab.

#### D/A channel Manual-Calibration

- **Step 1:** Click the *Manual D/A Calibration* tab to show the D/A channel manual calibration panel. Two D/A channels are individually calibrated. Before calibrating, output desired voltage from the D/A channels and measure it through an external precision multimeter.

- **Step 2:** For example, choose channel 0; select the *Range* and select the wished output voltage code or value from the radio buttons (Fig. 5-17 and Fig. 5-18).

Figure 5-17 & Figure 5-18: Selecting D/A Range and Choosing Output Voltage

**Step 3:** According to the difference between the output voltage from D/A channel and the value in the multimeter, adjust the gain, bipolar offset and unipolar offset registers (Fig. 5-19)

Figure 5-19: Adjusting registers

**Step 4:** Adjust registers until they fall between the output voltage from the D/A channel and the value in the multimeter.

Chapter 5

This page is left blank on purpose.

# A. Specifications

## PCI-1710/1710L/1710HG/1710HGL

# **Analog Input:**

| Channels                        |      | 16 single-ended or 8 differential or combination                                |         |          |                 |           |          |           |          |       |        |  |

|---------------------------------|------|---------------------------------------------------------------------------------|---------|----------|-----------------|-----------|----------|-----------|----------|-------|--------|--|